# Towards Offloading C/C++ Kernels and ONNX Models to CGRAs through MLIR

Nelson Neto<sup>1,2</sup>, José Pedro Ferreira<sup>1,2</sup>, Pedro Gonçalo Correia<sup>1,2</sup>, Juan Gallego<sup>3</sup>, Alfonso Rodríguez<sup>3</sup>, Andrés Otero<sup>3</sup>, Nuno Paulino<sup>1,2</sup>, João Bispo<sup>1,2</sup>

## Motivation

Offloading edge AI applications to CGRAs is convenient because:

- Increasing edge AI applications requires efficient execution platforms.

- GPUs and FPGAs present scalability and energy-consumption challenges.

- CGRAs offer promising performance-energy balance for edge AI.

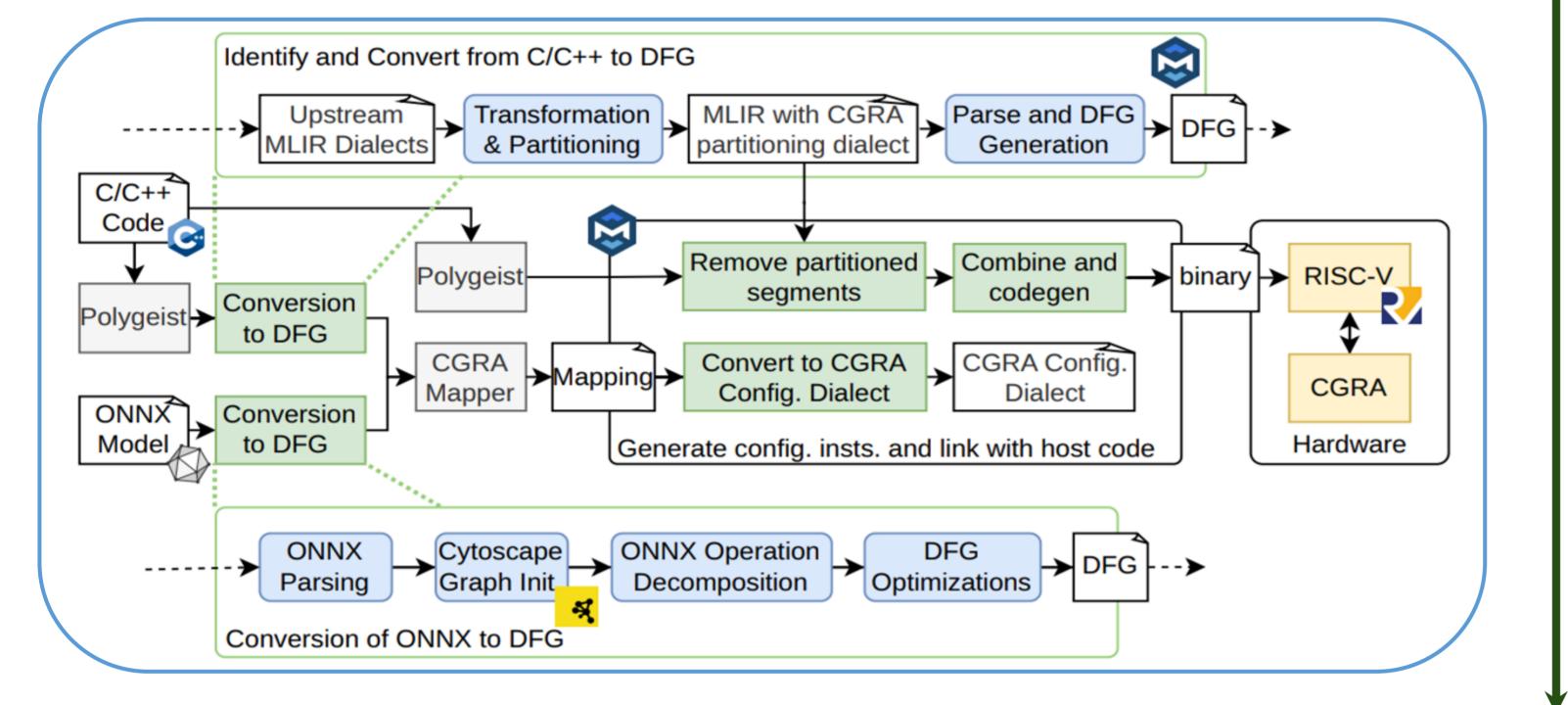

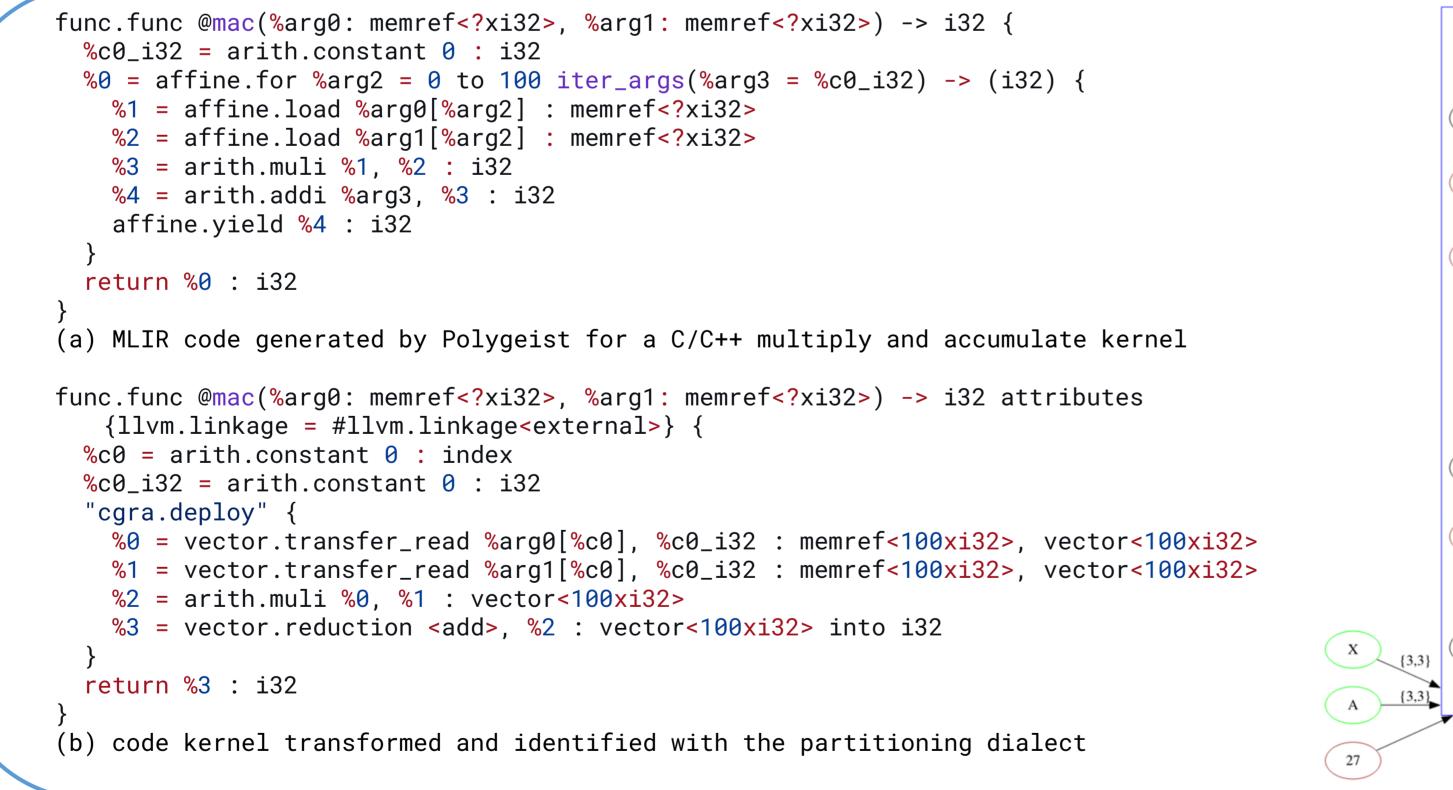

## C/C++ Path: MLIR Dialect for DFG Extraction

- Polygeist tool converts source code to MLIR.

- MLIR-based extraction of vectorized computation kernels as Data Flow Graphs (DFGs).

- Custom MLIR dialect identifies operations compatible with available CGRA processing elements for acceleration.

## **Architecture Diagram**

## **ONNX Path: Operation Decomposition**

- Direct ONNX parsing into structured JSON objects and Cytoscape graphs.

- Decomposition of high-level ONNX operations (like MatMul) into lower-level arithmetic/memory operations.

- Generation of detailed DFGs, suitable for mapping onto CGRA.

## **Key Contributions**

- Unified MLIR-based compilation workflow targeting both C/C++ kernels and ONNX AI models for CGRA acceleration.

- Preserves high-level graph semantics throughout compilation, enhancing opportunities for optimization and debugging.

- Seamless integration of CGRA configuration instructions directly into RISC-V executable binaries, removing the need for external configuration memory.

- Streamlines the deployment process and accelerates the practical adoption of edge AI applications.

#### Results - Data Flow Graphs suitable for CGRA Mapping

Addition Multiplication Multiplication Multiplication

**Ongoing Work**

Conclusion

- Improving automatic identification and partitioning of CGRA-compatible computations.

- Implementing more powerful loop-level optimizations in the MLIR dialect.

- Extending ONNX support for diverse tensor operations.

- Refining validation methods.

This workflow successfully unifies compilation of C/C++ kernels and ONNX models into a common graph format for CGRA acceleration. By preserving high-level semantics and embedding configuration directly in RISC-V binaries, it simplifies deployment and enhances edge AI performance, but can still be further optimized and extended.

Supported by Chips Joint Undertaking (Chips JU) and National

Supported by Fundação para a Ciência e Tecnologia (FCT) PhD scholarship 2024.05584.BDANA

Project PCI2022-135077-2 funded by MICIU/AEI /10.13039/501100011033 and by European Union NextGenerationEU/PRTR (nº 101096658)